AD5932是一款提供可编程频率扫描的波形发生器。这款器件采用支持增强型频率控制的嵌入式数字处理技术,能够生成合成的模拟或数字频率步进波形。采用预先编程的频率配置文件可以避免连续的写周期,从而释放了重要的DSP/微控制器资源。波形从已知相位开始,并可以连续地增加相位,因此能够轻松的确定相移。AD5932功耗仅为6.7 mA,为波形产生提供方便的低功耗解决方案。

英文Datasheet:下载链接

目录 · Table of Contents

简介和描述

AD5932产品特征:

- 可编程频率配置文件;无需外部元件

- 输出频率高达25 MHz

- 预编程的频率配置文件能将DSP/微控制器的写操作次数减到最少

- 正弦波/三角波/方波输出

- 频率步进的自动或单引脚控制

- 关断模式:20 µA

- 电源:2.3 V至5.5 V

- 应用温度范围:-40°C至+125°C

- 16引脚、无铅TSSOP封装

可用于:

- 频率扫描/雷达

- 网络/阻抗测量

- 增量式频率激励

- 传感器应用 – 近距和运动

AD5932在目标范围内的定义时长内输出各频率,然后在扫描范围内步入下一频率。可对该器件输出特定频率的时长进行预先编程并让器件自动递增该频率;或者,频率通过CTRL引脚进行外部递增。在范围结束时,AD5932继续输出最后一个频率直至重置器件。另外,AD5932还通过MSBOUT引脚提供数字输出。

对AD5932进行编程时,用户需要输入起始频率、频率步进、增量数量,以及器件输出各频率的时间间隔。频率扫描配置文件可通过切换CTRL引脚来启动和执行。

AD5932通过三线式串行接口写入数据,能够在高达40 MHz的时钟速率下工作。该器件采用2.3 V至5.5 V电源供电。

请注意,AVDD和DVDD彼此独立并可采用不同的电压工作。AD5932还具有待机功能,能够关断器件中没有使用的部分。

AD5932提供16引脚、无铅TSSOP封装。

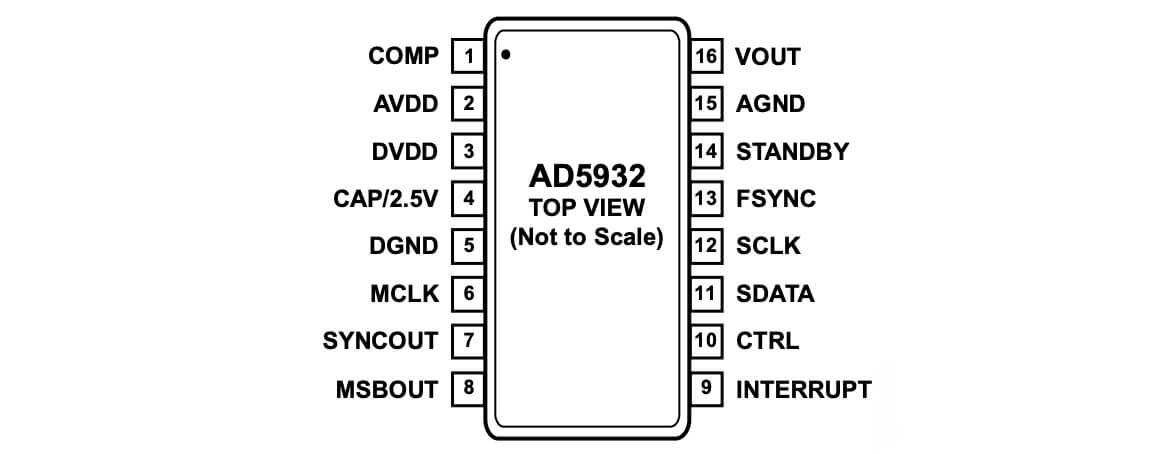

引脚配置和功能说明

| 引脚 | 助记符 | 描述 |

| 1 | COMP | DAC偏置引脚。 该引脚用于将DAC偏置电压去耦至AVDD。 |

| 2 | AVDD | 模拟部分的正向电源。 AVDD的值可以在2.3 V至5.5 V之间。0.1µF去耦电容应连接在AVDD和AGND之间。 |

| 3 | DVDD | 数字部分的正向电源。 DVDD的值可以在2.3 V至5.5 V之间。0.1µF去耦电容应连接在DVDD和DGND之间。 |

| 4 | CAP/2.5V | 数字电路。 使用2.5 V电源供电。 该2.5 V是使用板载DVDD产生的调节器。 稳压器需要一个通常为100 nF的去耦电容器,该电容器从CAP / 2.5V连接至DGND。 如果DVDD等于或小于2.7 V,则CAP / 2.5V可以与DVDD短路。 |

| 5 | DGND | 所有数字电路的接地。 |

| 6 | MCLK | 数字时钟输入。 DDS输出频率表示为MCLK频率的二进制分数。输出频率精度和相位噪声由该时钟确定。 |

| 7 | SYNCOUT | 扫描状态信息的数字输出。 用户可选择扫描结束(EOS)或通过以下方式增加频率控制寄存器(SYNCOP位)。 必须通过将控制寄存器中的SYNCOUTEN位置1来使能此引脚。 |

| 8 | MSBOUT | 数字输出。 DAC数据的反相MSB在该引脚上可用。 此输出引脚必须通过以下方式启用将控制寄存器中的MSBOUTEN位置1。 |

| 9 | INTERRUPT | 数字输入。 该引脚在频率扫描期间用作中断。 从低到高的过渡由内部MCLK,用于重置内部状态机。 这导致DAC输出达到中间电平。 |

| 10 | CTRL | 数字输入。 三功能引脚,用于初始化,启动和外部频率增量。 从低到高内部MCLK采样的转换用于初始化和启动内部状态机,然后执行预编程的频率扫描序列。 在自动递增模式下,单个脉冲执行整个扫描顺序。 在外部增量模式下,每个频率增量由低到高触发过渡。 |

| 11 | SDATA | 串行数据输入。 16位串行数据字首先通过寄存器地址施加到该输入,然后是数据的MSB到LSB。 |

| 12 | SCLK | 串行时钟输入。 在每个SCLK下降沿将数据输入AD5932。 |

| 13 | FSYNC | 低电平有效控制输入。 这是串行数据的帧同步信号。 当FSYNC设为低电平时,内部逻辑被告知有一个新字正在加载到设备中。 |

| 14 | STANDBY | 高电平有效输入。 当该引脚为高电平时,内部MCLK被禁用,参考DAC和调节器断电。 为了实现最佳的省电效果,建议将AD5932复位后再投入使用待机状态,因为这会导致典型的20微安的停机电流。 |

| 15 | AGND | 所有模拟电路的接地。 |

| 16 | VOUT | 电压输出。 AD5932的模拟输出可在此处获得。 不需要外部电阻负载,因为该器件板上有一个200Ω电阻。 建议在AGND上接一个20 pF的电容,以用作低通过滤并减少时钟馈通。 |

术语

积分非线性(INL)

积分非线性是任何代码的最大偏差从通过端点的直线转换功能。 传递函数的端点是零刻度和满刻度。 误差以LSB表示。

微分非线性(DNL)

微分非线性是被测物之间的差异DAC中两个相邻代码之间的理想1 LSB变化。规定的最大±1 LSB的差分非线性确保单调性。

无杂散动态范围(SFDR)

谐波基本频率和这些频率的图像,与目标频率一起展现在DDS设备的输出中。SFDR是指目标频段中存在的最大杂散或谐波。 宽带SFDR给出相对于0至Nyquist带宽中基频的最大谐波或杂散的幅度。窄带SFDR可在基频附近±200 kHz的带宽内衰减最大杂散或谐波。

总谐波失真(THD)

总谐波失真是谐波均方根和与基波均方根值之比。 对于AD5932,THD定义为:

其中:V_1是基波的均方根幅度;V_{2-6}是六次谐波的均方根幅度。

信噪比(SNR)

信噪比是测得的输出信号的均方根值与奈奎斯特频率以下的所有其他频谱分量的均方根和的比率。 SNR值以dB表示。

时钟馈通

从MCLK输入到模拟输出之间有馈通。 时钟馈通是指MCLK信号相对于AD5932输出频谱中基频的幅度。

操作理论

AD5932是一款通用的合成波形发生器,能够在频域和时域提供数字可编程波形序列。

该设备包含嵌入式数字处理,以提供用户可编程频率曲线的扫描,从而增强了频率控制。 由于该器件是可预编程的,因此消除了DSP /微控制器在生成特定波形时的连续写入周期。

频率曲线

频率曲线由起始频率(F_{\operatorname{START}})定义,频率增量(\Delta{f})和每次扫描的增量数(N_{\operatorname{INCR}})。 频率增量之间的增量间隔t_{\operatorname{INT}}可以由用户编程,间隔由设备自动确定(自动增量模式),也可以通过硬件引脚从外部控制(外部增量模式)。 对于自动更新,间隔配置文件可以使用固定数量的时钟周期或固定数量的输出波形周期。

在自动递增模式下,CTRL引脚上的单个脉冲开始并执行频率扫描。 在外部递增模式下,CTRL引脚也开始扫描,但是频率递增间隔由CTRL引脚上连续的0/1跳变之间的时间间隔确定。

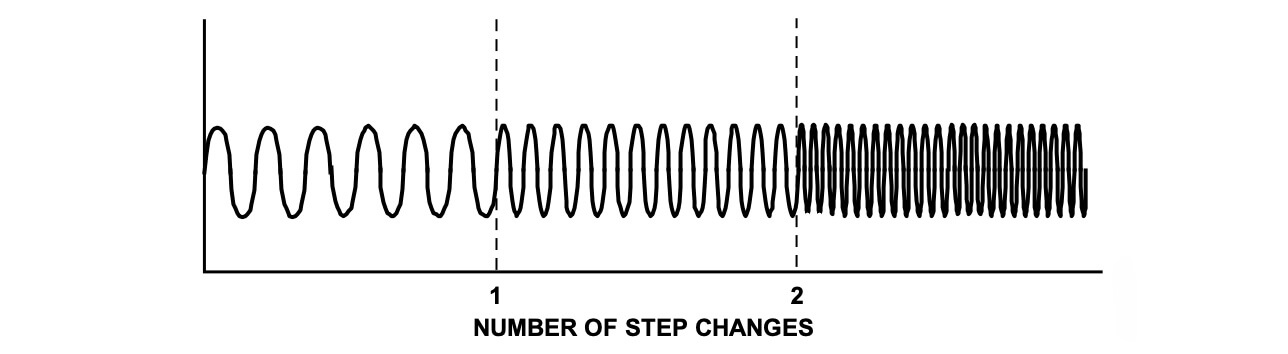

两步频率扫描的示例如下图所示。请注意,扫频输出信号是连续可用的,因此在所有频率增量处都是连续的。

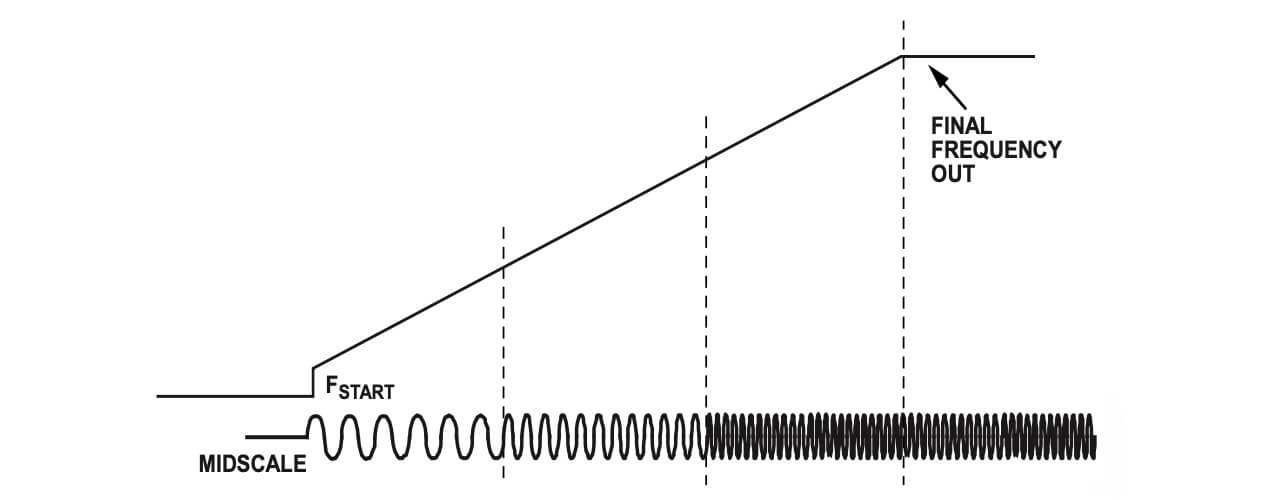

当AD5932完成从频率开始到频率结束,即从F_{\operatorname{START}}递增到F_{\operatorname{START}}+N_{\operatorname{INCR}}+\Delta{f},的频率扫描时,它将继续输出扫描中的最后一个频率(见下图)。 请注意,频率扫描时间由((N_{\operatorname{INCR}}+1)\times t_{\operatorname{INT}})给出。

串行接口

AD5932具有一个标准的3线串行接口,该接口与SPI®,QSPI™,MICROWIRE™和DSP标准接口兼容。

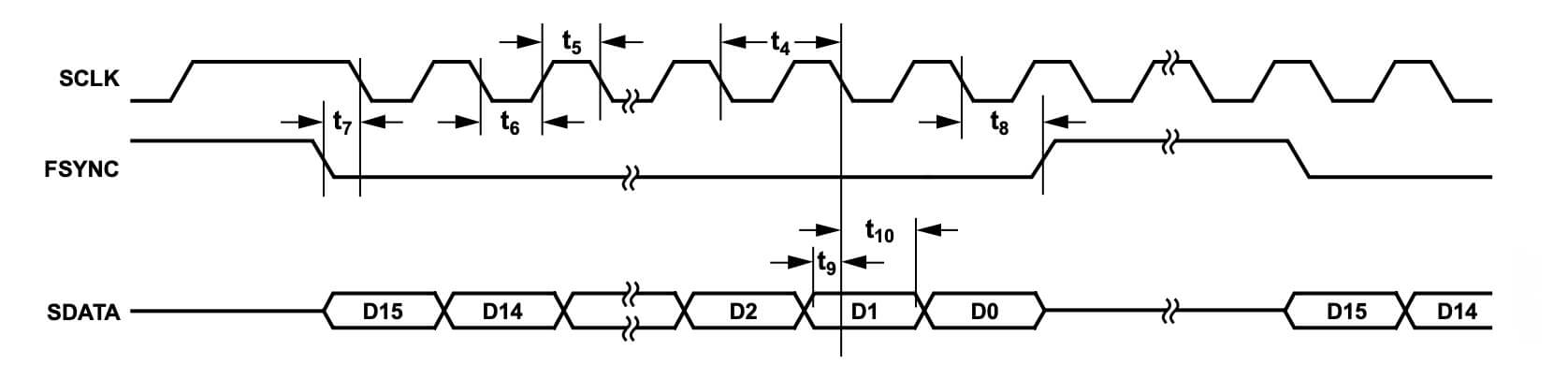

在串行时钟输入SCLK的控制下,数据以16位字的形式加载到器件中。 此操作的时序图如下图所示。

FSYNC输入是电平触发输入,用作帧同步和芯片使能。 仅当FSYNC为低电平时,数据才能传输到设备中。 要开始串行数据传输,应将FSYNC设为低电平,并遵守最小的FSYNC至SCLK下降沿建立时间t_7。 FSYNC变为低电平后,串行数据在SCLK的下降沿移入器件的输入移位寄存器,持续16个时钟脉冲。 在SCLK的第16个下降沿之后,FSYNC可能会变高,观察到FSYNC上升沿时间t_8的最小SCLK下降沿。 另外,对于16个SCLK脉冲,FSYNC可以保持低电平,然后在数据传输结束时将其拉高。 这样,可以在FSYNC保持为低电平的同时加载16位字的连续流。 只有在加载了最后一个字的第16个SCLK下降沿之后,FSYNC才应变为高电平。

SCLK可以是连续的,或者,SCLK可以是连续的写操作之间的空闲高电平或低电平。

AD5932上电

AD5932上电后,该器件处于不确定状态,因此必须在使用前复位。 七个寄存器(控制和频率)包含无效数据,用户需要将其设置为已知值。

控制寄存器应该是要编程的第一个寄存器,因为这将配置芯片设置。 注意,对控制寄存器的写操作会自动复位内部状态机,并提供中等规模的模拟输出,因为它执行的功能与INTERRUPT引脚相同。 通常,这之后是所有必需扫描参数的串行加载。 DAC输出保持在中间电平,直到使用CTRL引脚开始频率扫描为止。

AD5932编程

AD5932设计用于在触发CTRL引脚时提供自动频率扫描。 扫描由一组寄存器控制,其地址在下表中给出。每个寄存器的功能在“设置频率扫描”部分中有更详细的描述。

| D15 | D14 | D13 | D12 | 助记符 | 名称 |

| 0 | 0 | 0 | 0 | C_{\operatorname{REG}} | 控制位 |

| 0 | 0 | 0 | 1 | N_{\operatorname{INCR}} | 增量数 |

| 0 | 0 | 1 | 0 | \Delta_{f} | 低12位增量频率 |

| 0 | 0 | 1 | 1 | \Delta_{f} | 高12位增量频率 |

| 0 | 1 | t_{\operatorname{INT}} | 增量间隔 | ||

| 1 | 0 | 预留位 | |||

| 1 | 1 | 0 | 0 | F_{\operatorname{START}} | 低12位起始频率 |

| 1 | 1 | 0 | 1 | F_{\operatorname{START}} | 高12位起始频率 |

| 1 | 1 | 1 | 0 | 预留位 | |

| 1 | 1 | 1 | 1 | 预留位 |

控制寄存器

AD5932包含一个12位控制寄存器,用于设置工作模式,如下图所示。

| D15 | D14 | D13 | D12 | D11至D0 |

| 0 | 0 | 0 | 0 | 控制位 |

该寄存器控制AD5932的不同功能和各种输出选项。 表6描述了控制寄存器的各个位。

要寻址控制寄存器,16位串行的D15至D12字必须设置为0。

| 位 | 名称 | 功能 |

| D15至D12 | ADDR | 寄存器地址位 |

| D11 | B24 | 需要两个写操作才能将完整的字加载到F_{\operatorname{START}}寄存器和\Delta{f}寄存器中。 当B24 = 1时,两个连续的写操作会将一个完整的字加载到频率寄存器中。 第一次写入包含频率字的12个LSB,而下次写入包含12个MSB。 有关适当的地址,请参见表5。 在两个字都装入之后,才进行对目标寄存器的写操作,因此该寄存器永远不会保存中间值。 当B24 = 0时,24位F_{\operatorname{START}}/\Delta{f} 寄存器用作两个12位寄存器,一个包含12个MSB,另一个包含12个LSB。 这意味着可以独立于12个LSB更改频率字的12个MSB,反之亦然。 如果不需要完整的24位更新,这将很有用。 要更改12个MSB或12个LSB,只需对相应的寄存器地址进行一次写操作。 有关适当的地址,请参见表“寄存器地址”。 |

| D10 | DAC ENABLE | DAC ENABLE = 1时,使能DAC。 当DAC ENABLE = 0时,DAC掉电。 这样可以节省功率,并且在仅使用DAC输入数据的MSB(可从MSBOUT引脚获得)时很有用。 |

| D9 | SINE/TRI | 该位的功能是控制VOUT引脚上的可用引脚。 当SINE / TRI = 1时,SIN ROM用于将相位信息转换为幅度信息,从而在输出端产生正弦信号。 当SINE / TRI = 0时,将绕过SIN ROM,从而导致DAC输出为三角形(上下)。 |

| D8 | MSBOUTEN | 当MSBOUTEN = 1时,MSBOUT引脚使能。 当MSBOUTEN = 0时,MSBOUT被禁用(三态)。 |

| D7 | 预留位 | 该位必须设置为1 |

| D6 | 预留位 | 该位必须设置为1 |

| D5 | INT/EXT INCR | 当INT / EXT INCR = 1时,频率增量通过CTRL引脚从外部触发。 当INT / EXT INCR = 0时,频率增量会自动触发。 |

| D4 | 预留位 | 该位必须设置为1 |

| D3 | SYNCSEL | 当D2 = 1时,该位有效。用户可以选择在扫描结束(EOS)时或在每个频率增量处发出脉冲。 当SYNCSEL = 1时,SYNCOUT引脚在扫描结束时输出高电平,并在随后的扫描开始时返回0。 当SYNCSEL = 0时,SYNCOUT仅在每个频率增量上输出4 \times T_{\operatorname{CLOCK}}脉冲。 |

| D2 | SYNCOUTEN | 当SYNCOUTEN = 1时,SYNC输出可通过SYNCOUT两端获得。 当SYNCOUTEN = 0时,SYNCOP插入被补充(三态)。 |

| D1 | 预留位 | 该位必须设置为1 |

| D0 | 预留位 | 该位必须设置为1 |

设置频率扫描

如“频率曲线”部分所述,AD5932需要对某些寄存器进行编程以启用频率扫描。下文将更详细地讨论这些寄存器。

起始频率

要开始频率扫描,用户需要告知AD5932从哪个频率开始扫描。 该频率存储在一个名为F_{\operatorname{START}}的24位寄存器中。 如果用户希望更改FSTART寄存器的全部内容,则必须执行两次连续写入:一次写入LSB,另一次写入MSB。

请注意,对于整个对该寄存器的写入,应将控制位B24(D11)设置为1,首先对LSB进行编程。